IC Design

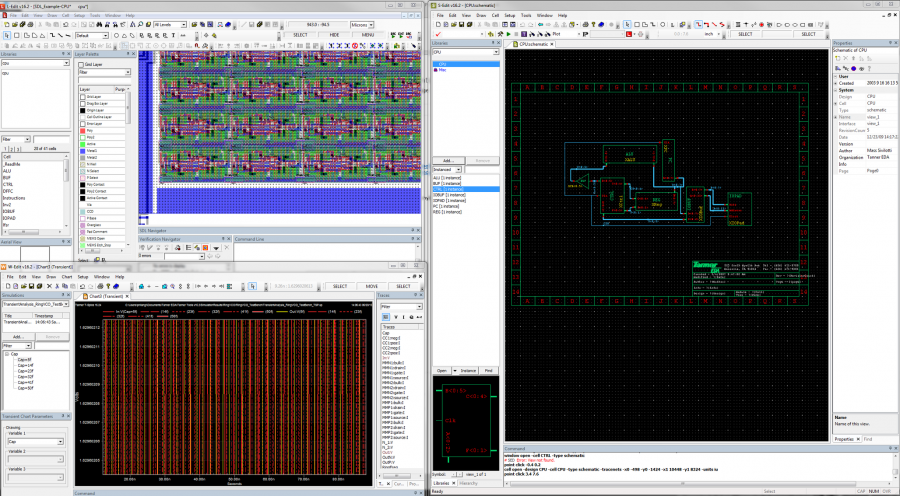

Tanner Analog/Mixed-Signal IC Design Flow

O Software Tanner EDA AMS oferece um ambiente completo de desenvolvimento de circuitos integrados analógicos, de sinal misto, digital, RF, Photonics, MEMS. O fluxo de projetos é otimizado CIs analógicos customizados ou CIs de sinal misto “analógico no topo”, trabalhando com tecnologias acima de 28nm. Este fluxo é utilizado em uma infinidade de mercados incluindo: automotivo, internet das coisas (IoT), imagem/display, controle industrial, médico, sensores, RF, espacial, e gerenciamento de potência

Características e benefícios:

- Fluxo completo analógico e de sinal misto

- Database nativa OpenAccess

- Simulação combina netlists em vários níveis de abstração: modelos comportamentais, RTL nível de bloco, blocos a nível de gates e transistores

- Debug e verificação avançada com SystemVerilog, Verilog, Verilog-AMS, Verilog-A e VHDL.

- Editor de layout rule-aware

- Roda Calibre® nmDRC™, nmLVS™,

- RVE™, xRC™, xACT™, 3DSTACK™,

- PERC™, DFM™ diretamente do L-Edit

- Fluxo digital com o Oasys™ synthesis e Nitro™ place e route

- Análise te tempo estático com o Optimus™

- Interface de controle de revisão flexível incluindo integração com o ClioSoft®

- PDK - Suporte as mais importantes foundries do mercado

- Disponível em Linux e Windows

- Uso intuitivo e fácil, curva rápida de aprendizado.